I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

BMP file bitmap image read using TEXTIO

Converting the image file to a bitmap format makes for the easiest way to read a picture using VHDL. Support for the BMP raster graphics image file format is built into the Microsoft Windows operating system. That makes BMP a suitable image format for storing photos for use in VHDL testbenches. In this article, you…

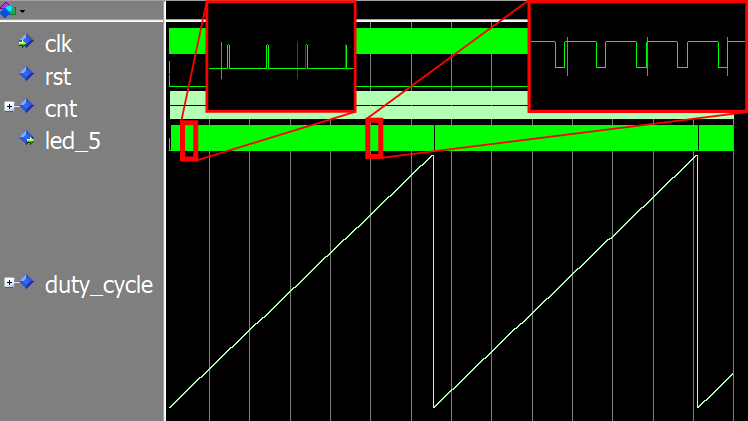

How to create a PWM controller in VHDL

Pulse-width modulation (PWM) is an efficient way to control analog electronics from purely digital FPGA pins. Instead of attempting to regulate the analog voltage, PWM rapidly switches on and off the supply current at full power to the analog device. This method gives us precise control over the moving average of energy provided to the…

How to delay time in VHDL: Wait For

In the previous tutorial we learned that a process can be thought of as a program thread. We also learned that a wait; statement causes the program to pause indefinitely. But is there a way to make a program wait for any other time value than forever? If we remove the wait; altogether and try…

How to use Port Map instantiation in VHDL

A module is a self-contained unit of VHDL code. Modules communicate with the outside world through the entity. Port map is the part of the module instantiation where you declare which local signals the module’s inputs and outputs shall be connected to. In previous tutorials in this series we have been writing all our code…

How to use a Case-When statement in VHDL

The Case-When statement will cause the program to take one out of multiple different paths, depending on the value of a signal, variable, or expression. It’s a more elegant alternative to an If-Then-Elsif-Else statement with multiple Elsif’s. Other programming languages have similar constructs, using keywords such as a switch, case, or select. Among other things,…

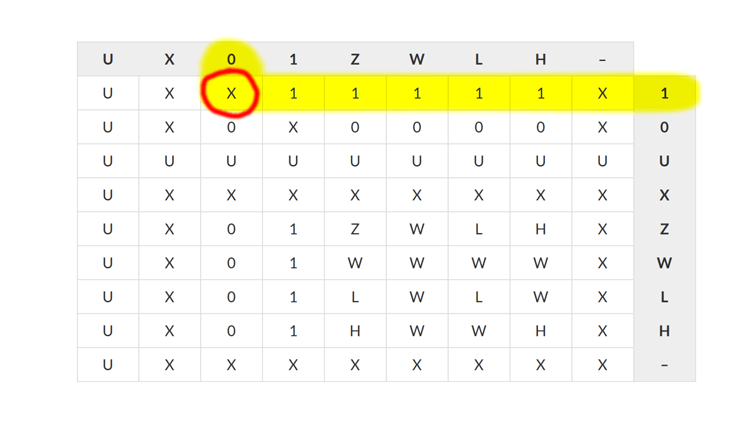

std_logic vs std_ulogic

VHDL includes few built-in types but offers several additional types through extension packages. Two of the most widely used types are std_logic and std_ulogic. The difference between them is that the former is resolved while the latter isn’t. Before we go on to investigate what it means that a type is resolved, let’s first look…

First of all, thank you so very much!

These are by far the most comprehensible tutorials I have come across like ever!

Brilliant work.

So here my two cents out of gratitude:

Basic VHDL Quiz – part 4

Which statement is not true?

Answer 3 : The return statement cannot be omitted.

-> Correct

So the return statement CAN be omitted???

“Unlike in most other programming languages, the return keyword is mandatory in functions in VHDL.”

Confused by double negation. Me or you 😉

Good catch! I’ve changed the answer now. I was trying to make you think, but in the process I confused myself too 🙂

“The return-keyword cannot be used in a procedure”. I believe that this is incorrect, e.g.

https://web.archive.org/web/20200629023040/http://vhdl.renerta.com:80/source/vhd00060.htm

It is true, of course, that you cannot return a value with it, that’s the only (?) difference between procedures and functions. But, as in other languages, you can use “return” as control flow statement to “force an exit”.

You are right! I missed the possibility of using return statements in procedures without returning a value. According to the Renata link you posted, functions must return a value, while procedures can have return statements, but then without a return value.

I am changing this question.