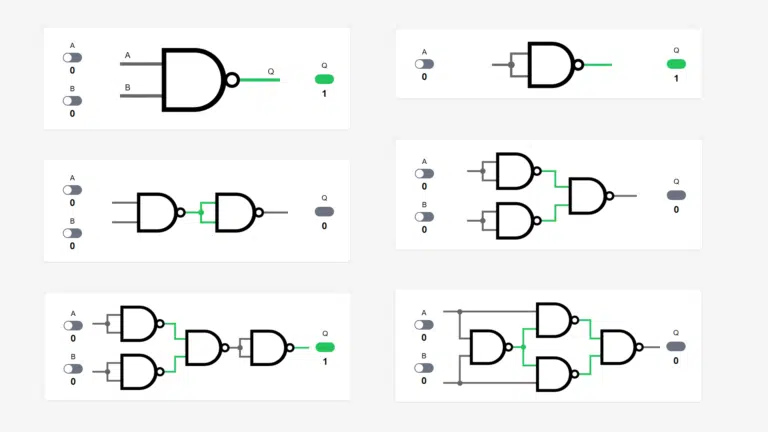

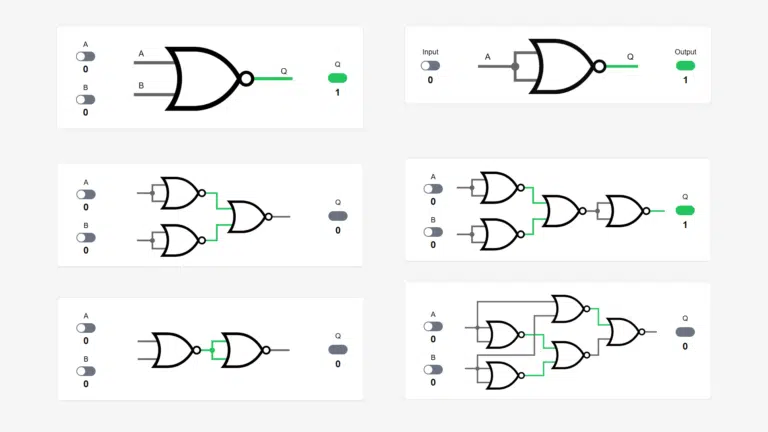

NAND logic gates interactive demo

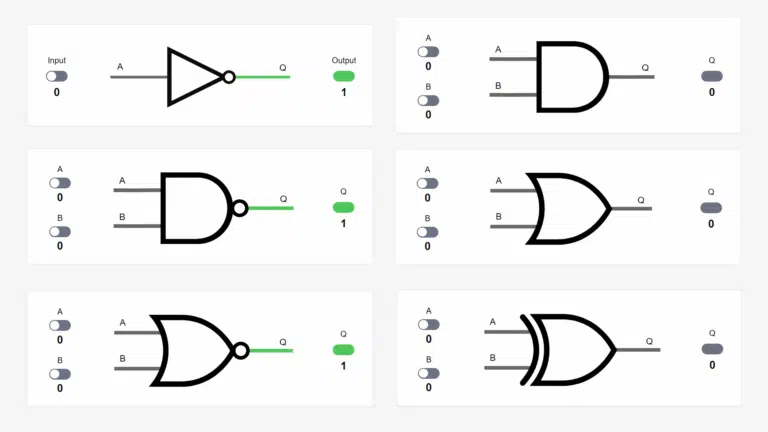

We can construct any other digital logic gate using only NAND gates as building blocks. This is why NAND is known as a universal gate. NAND logic is widely used as the foundation for designing digital circuits in modern integrated chips. Actually, NOR is also a universal gate, but NAND logic is more prevalent than…