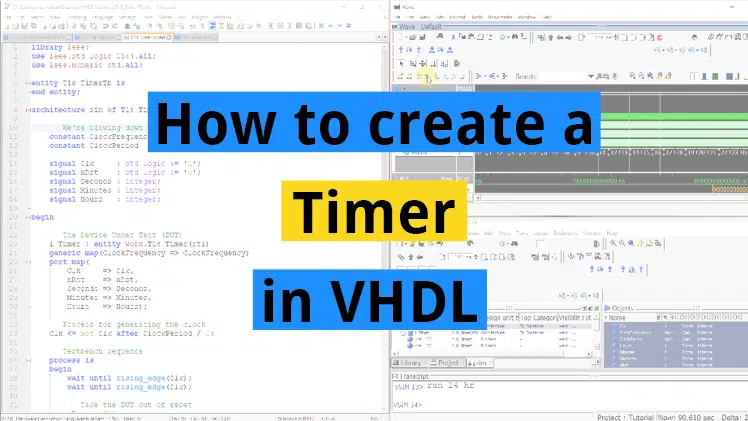

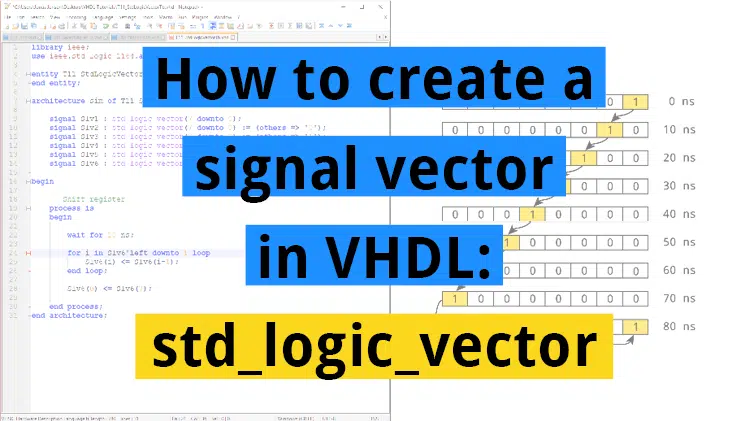

How to create a timer in VHDL

In earlier tutorials we have used the wait for statement to delay time in simulation. But what about production modules? The wait for statement cannot be used for that. That only works in simulation because we can’t just tell the electrons in a circuit to pause for a given time. So how can we keep…