I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to install a VHDL simulator and editor for free

Although VHDL and FPGA tools are often very expensive, it is easy to access state-of-the-art software for free if you are a student. There are several simulators, editors, and IDEs for working with VHDL. This article shows you how to install two of the most popular programs used by VHDL engineers. VHDL simulator Siemens EDA’s…

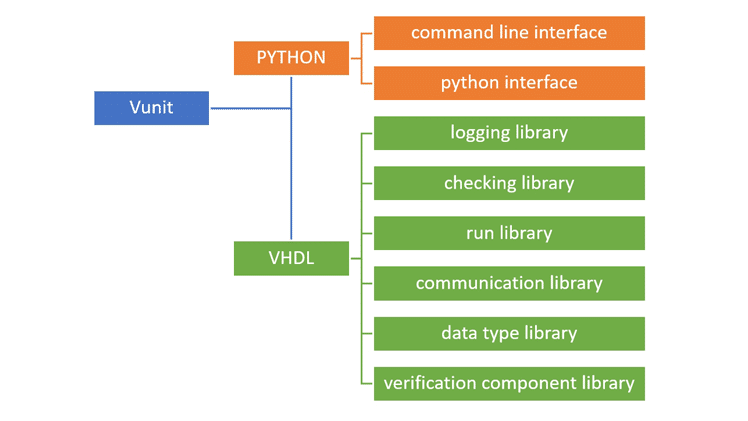

Getting started with VUnit

VUnit is one of the most popular open-source VHDL verification frameworks available today. It combines a Python test suite runner with a dedicated VHDL library to automate your testbenches.

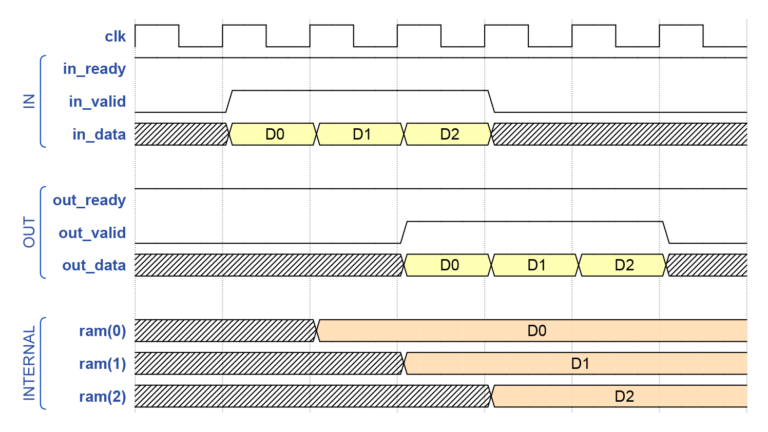

How to make an AXI FIFO in block RAM using the ready/valid handshake

I was a little annoyed by the peculiarities of the AXI interface the first time I had to create logic to interface an AXI module. Instead of the regular busy/valid, full/valid, or empty/valid control signals, the AXI interface uses two control signals named “ready” and “valid”. My frustration soon changed to awe. The AXI interface…

Should I learn VHDL if Verilog is becoming more popular?

Which HDL is the most popular, and should I learn VHDL or Verilog? That’s a question I often get asked, and it’s understandable. People want to future-proof their learning by betting on the winning horse. But which one is it, and does it matter?

Basic VHDL quiz – Part 4

Test your progress with this VHDL quiz after completing part 4 of the Basic VHDL Tutorial series!

How to create a process with a sensitivity list in VHDL

You should always use a sensitivity list to trigger processes in production modules. Sensitivity lists are parameters to a process which lists all the signals that the process is sensitive to. If any of the signals change, the process will wake up, and the code within it is executed. We’ve already learned to use the…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.