I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

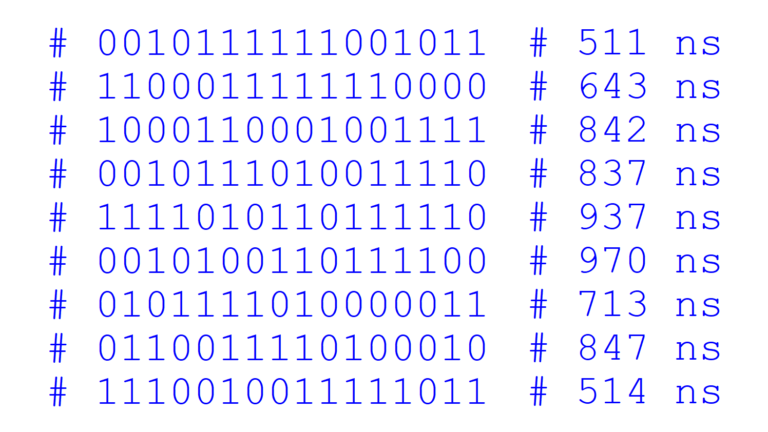

How to generate random numbers in VHDL

VHDL has a built-in pseudo-random generator, but it can only generate floating-point numbers between 0 and 1. Fortunately, you can derive from this any other kind of random data format you should need. Continue reading this article to find out how to produce real or integer values of any range, as well as random std_logic_vector…

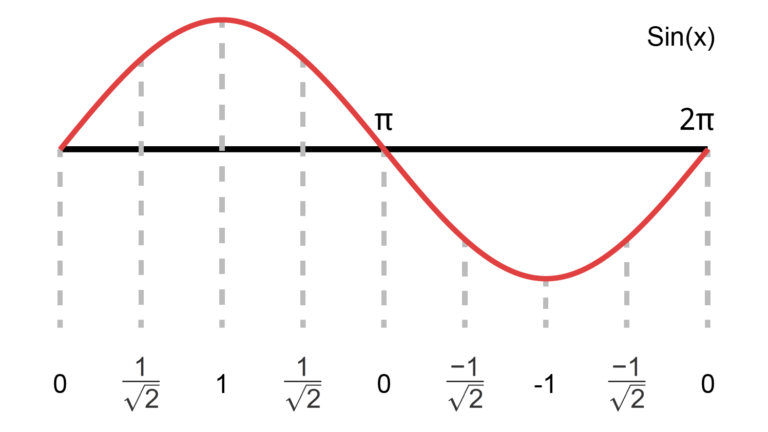

How to create a breathing LED effect using a sine wave stored in block RAM

I’ve noticed that many of the gadgets that I’ve bought the last couple of years have shifted away from LED blinking to led breathing. Most electronic gizmos contain a status LED whose behavior gives away indications of what’s going on inside of the device. My electric toothbrush flashes an LED when it’s time to recharge…

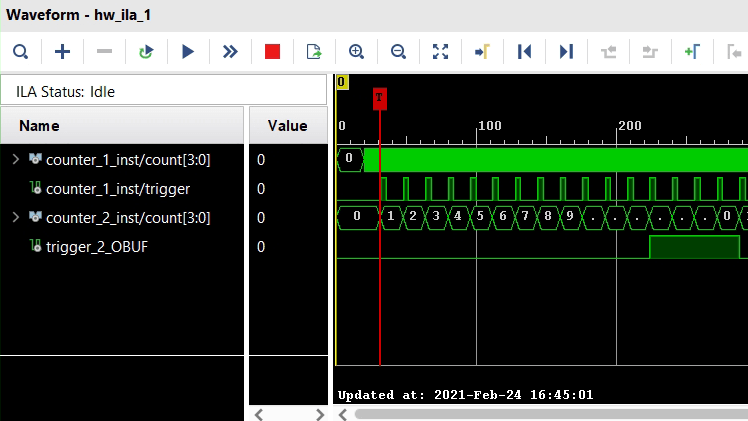

Using Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO)

This tutorial covers using the Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) cores to debug and monitor your VHDL design in the Xilinx Vivado IDE. In many cases, designers are in need to perform on-chip verification. That is, gaining access to an internal signal’s behavior in their FPGA design for verification purposes. One option…

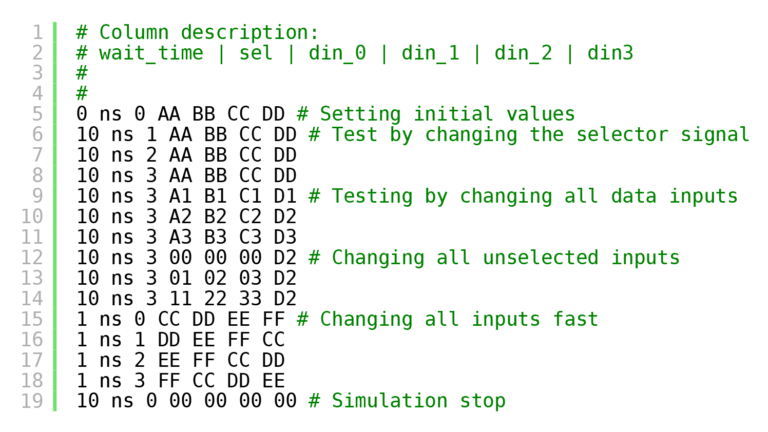

Stimulus file read in testbench using TEXTIO

Reading signal values from file is an alternative way of generating stimuli for the device on test (DUT). The testbench sequence and timing is hard-coded in a stimulus file that is read by the VHDL testbench, line by line. This allows you to easily change the pattern of the waveform that you want to feed…

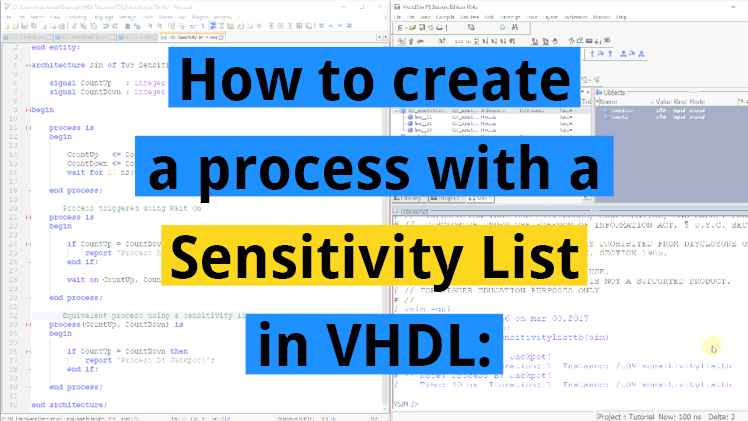

How to create a process with a sensitivity list in VHDL

You should always use a sensitivity list to trigger processes in production modules. Sensitivity lists are parameters to a process which lists all the signals that the process is sensitive to. If any of the signals change, the process will wake up, and the code within it is executed. We’ve already learned to use the…

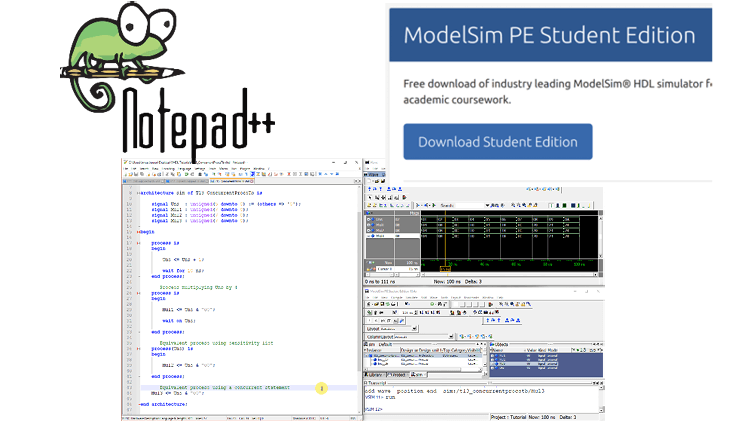

How to install a VHDL simulator and editor for free

Although VHDL and FPGA tools are often very expensive, it is easy to access state-of-the-art software for free if you are a student. There are several simulators, editors, and IDEs for working with VHDL. This article shows you how to install two of the most popular programs used by VHDL engineers. VHDL simulator Siemens EDA’s…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.