I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

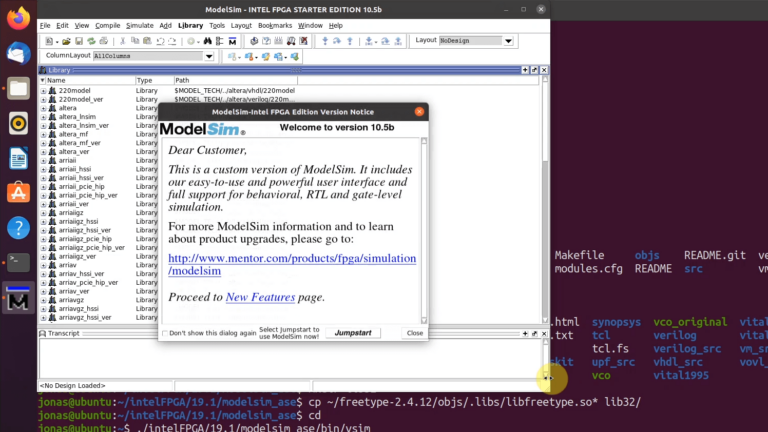

How to make ModelSim from Quartus Prime Lite work on Ubuntu 20.04

The ModelSim version that comes with Intel Quartus Prime Lite Edition is a good alternative if you want to try out VHDL simulation on your home computer. The software is available for both Windows and Linux, but Intel only supports Red Hat-based distros like CentOS Linux. Fortunately, you are just a few hacks away from…

How to create a self-checking testbench

A self-checking testbench is a VHDL program that verifies the correctness of the device under test (DUT) without relying on an operator to manually inspect the output. The self-checking testbench runs entirely on its own, and prints an “OK” or “Failed” message in the end. Every VHDL module should have an associated self-checking testbench. It’s…

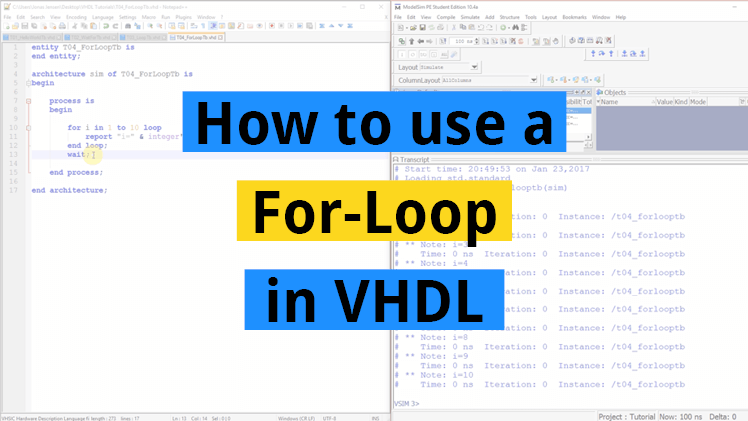

How to use a For loop in VHDL

In the previous tutorial we learned to create an infinite loop by using the loop statement. We also learned how the break out of a loop by using the exit statement. But what if we want the loop to iterate a certain number of times? The For-Loop is the easiest way to accomplish this. The…

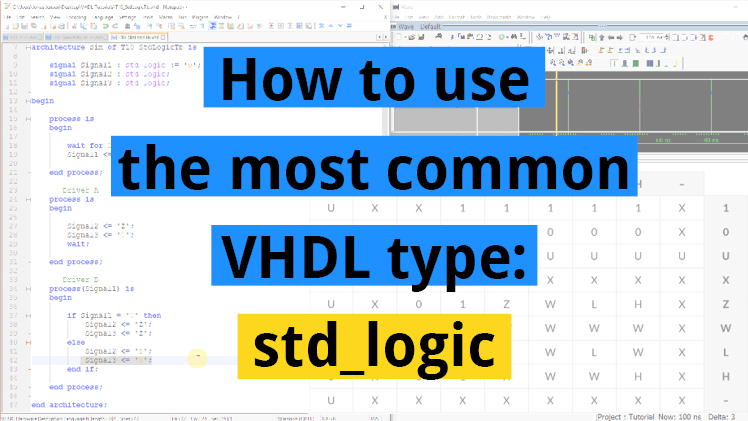

How to use the most common VHDL type: std_logic

The most common type used in VHDL is the std_logic. Think of this type as a single bit, the digital information carried by a single physical wire. The std_logic gives us a more fine-grained control over the resources in our design than the integer type, which we have been using in the previous tutorials. Normally,…

How to create a process with a sensitivity list in VHDL

You should always use a sensitivity list to trigger processes in production modules. Sensitivity lists are parameters to a process which lists all the signals that the process is sensitive to. If any of the signals change, the process will wake up, and the code within it is executed. We’ve already learned to use the…

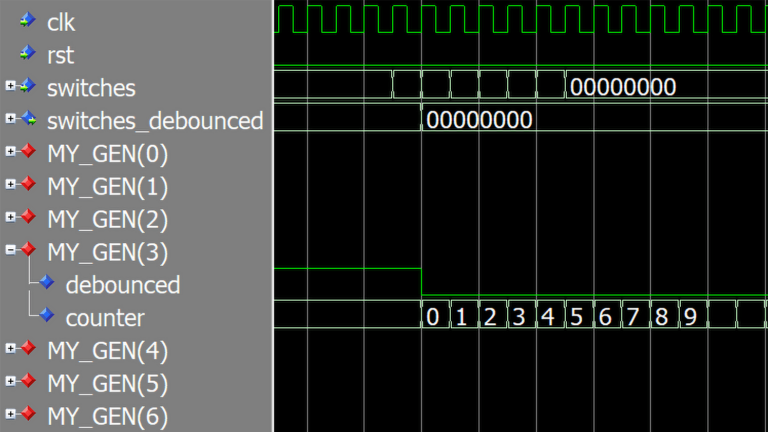

Generate statement debouncer example

The generate statement in VHDL can automatically duplicate a block of code to closures with identical signals, processes, and instances. It’s a for loop for the architecture region that can create chained processes or module instances.

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.