I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use Loop and Exit in VHDL

In the previous tutorial we learned how to delay time using the wait for statement. We also learned about the process loop. We now know that if we let it, the process “thread” will loop within the process forever. But what if we want to do something just once at the beginning of the process?…

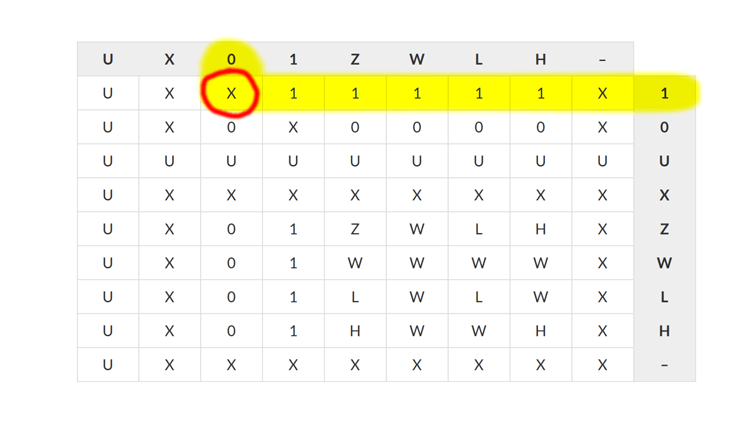

std_logic vs std_ulogic

VHDL includes few built-in types but offers several additional types through extension packages. Two of the most widely used types are std_logic and std_ulogic. The difference between them is that the former is resolved while the latter isn’t. Before we go on to investigate what it means that a type is resolved, let’s first look…

Basic VHDL quiz – Part 3

Test your progress with this VHDL quiz after completing tutorials 12-17 from the Basic VHDL Tutorial series!

Constrained random verification

Constrained random verification is a testbench strategy that relies on generating pseudo-random transactions for the device under test (DUT). The goal is to reach functional coverage of a number of predefined events through random interaction with the DUT. Open Source VHDL Verification Methodology (OSVVM) is a free VHDL library which includes a number of convenient…

How to use a For loop in VHDL

In the previous tutorial we learned to create an infinite loop by using the loop statement. We also learned how the break out of a loop by using the exit statement. But what if we want the loop to iterate a certain number of times? The For-Loop is the easiest way to accomplish this. The…

How to create a timer in VHDL

In earlier tutorials we have used the wait for statement to delay time in simulation. But what about production modules? The wait for statement cannot be used for that. That only works in simulation because we can’t just tell the electrons in a circuit to pause for a given time. So how can we keep…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.