I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Why you always need a testbench

As most hardware engineers, I started off my computer science career by learning a sequential programming language. The first language I learned at the University of Oslo was Java. While it’s not considered to be the most exciting language today, at the time, Java was at the pinnacle of its popularity. The engineers who built…

How to create a self-checking testbench

A self-checking testbench is a VHDL program that verifies the correctness of the device under test (DUT) without relying on an operator to manually inspect the output. The self-checking testbench runs entirely on its own, and prints an “OK” or “Failed” message in the end. Every VHDL module should have an associated self-checking testbench. It’s…

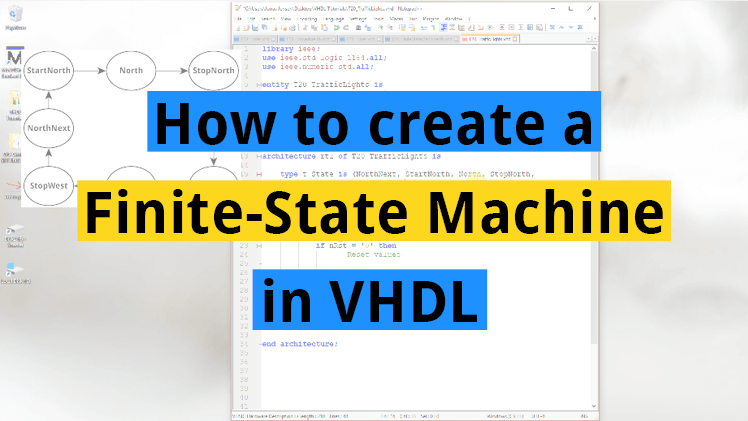

How to create a finite-state machine in VHDL

A finite-state machine (FSM) is a mechanism whose output is dependent not only on the current state of the input, but also on past input and output values. Whenever you need to create some sort of time-dependent algorithm in VHDL, or if you are faced with the problem of implementing a computer program in an…

How to create your first VHDL program: Hello World!

When learning a new programming language, I always like to start by learning how to print. When you master outputting “Hello World!”, you know that you’ve got the environment working. It also shows you the basic skeleton of the language, the bare minimum code required to produce any output. You might be thinking: but VHDL…

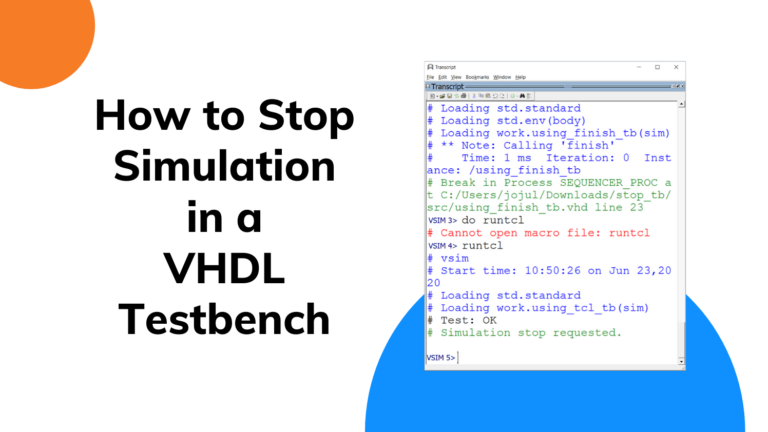

How to stop simulation in a VHDL testbench

How do you stop the VHDL simulator when the simulation is complete? There are several ways to do that. In this article, we will examine the most common ways to end a successful testbench run. The VHDL code presented here is universal, and it should work in any capable VHDL simulator. For the methods involving…

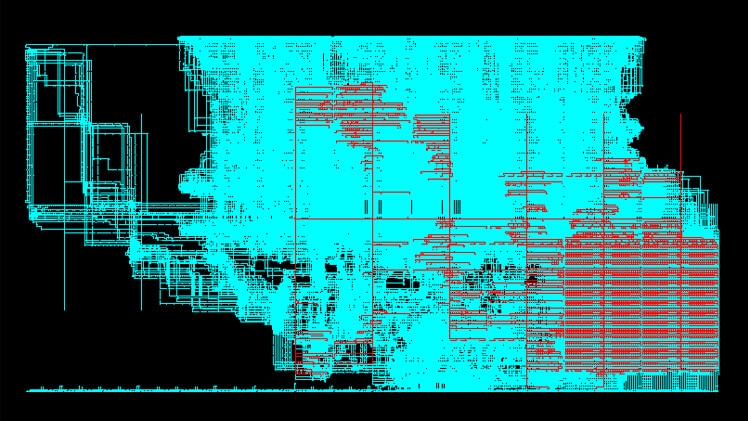

BMP file bitmap image read using TEXTIO

Converting the image file to a bitmap format makes for the easiest way to read a picture using VHDL. Support for the BMP raster graphics image file format is built into the Microsoft Windows operating system. That makes BMP a suitable image format for storing photos for use in VHDL testbenches. In this article, you…

First of all, thank you so very much!

These are by far the most comprehensible tutorials I have come across like ever!

Brilliant work.

So here my two cents out of gratitude:

Basic VHDL Quiz – part 4

Which statement is not true?

Answer 3 : The return statement cannot be omitted.

-> Correct

So the return statement CAN be omitted???

“Unlike in most other programming languages, the return keyword is mandatory in functions in VHDL.”

Confused by double negation. Me or you 😉

Good catch! I’ve changed the answer now. I was trying to make you think, but in the process I confused myself too 🙂

“The return-keyword cannot be used in a procedure”. I believe that this is incorrect, e.g.

https://web.archive.org/web/20200629023040/http://vhdl.renerta.com:80/source/vhd00060.htm

It is true, of course, that you cannot return a value with it, that’s the only (?) difference between procedures and functions. But, as in other languages, you can use “return” as control flow statement to “force an exit”.

You are right! I missed the possibility of using return statements in procedures without returning a value. According to the Renata link you posted, functions must return a value, while procedures can have return statements, but then without a return value.

I am changing this question.