Getting started with VUnit

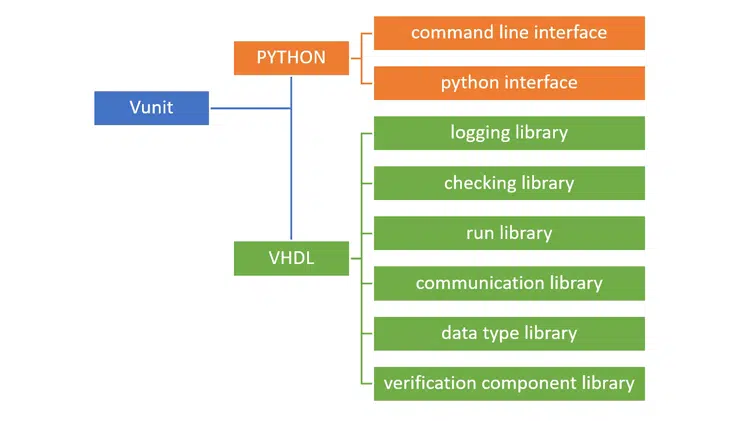

VUnit is one of the most popular open-source VHDL verification frameworks available today. It combines a Python test suite runner with a dedicated VHDL library to automate your testbenches.

VUnit is one of the most popular open-source VHDL verification frameworks available today. It combines a Python test suite runner with a dedicated VHDL library to automate your testbenches.

When designing VHDL for safety-critical FPGA applications, it’s not enough to write testbenches at best-effort. You have to present proof that the module works as intended and without undesirable side-effects. Formal verification techniques can help you map a requirement to a test, proving that your VHDL module conforms to the specification. It’s an instrumental tool…

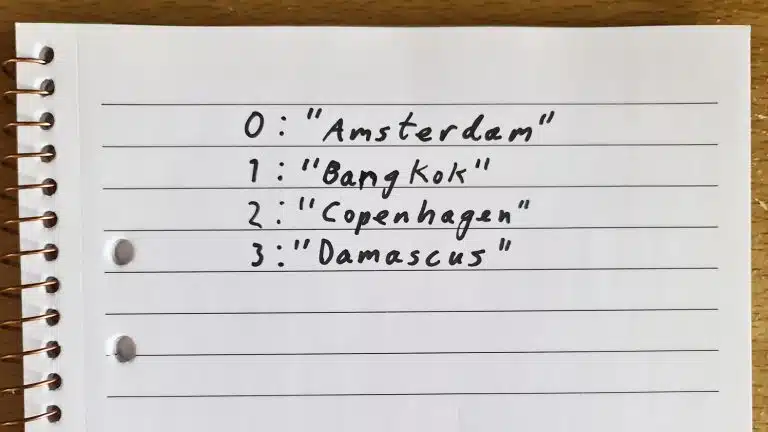

Text strings in VHDL are generally limited to fixed-length character arrays. That makes sense because VHDL describes hardware, and generic-length strings require dynamic memory. To define an array of strings, you have to allocate space at compile-time for the highest number of strings you want to store. Even worse, you must decide on the strings’…

This article examines how we can use configuration constructs to create variants of a module or testbench without maintaining multiple versions of the file. We will also look at other use cases for configuration declarations in VHDL design. Configurations have been part of the VHDL standard since the first version of the language. But still,…

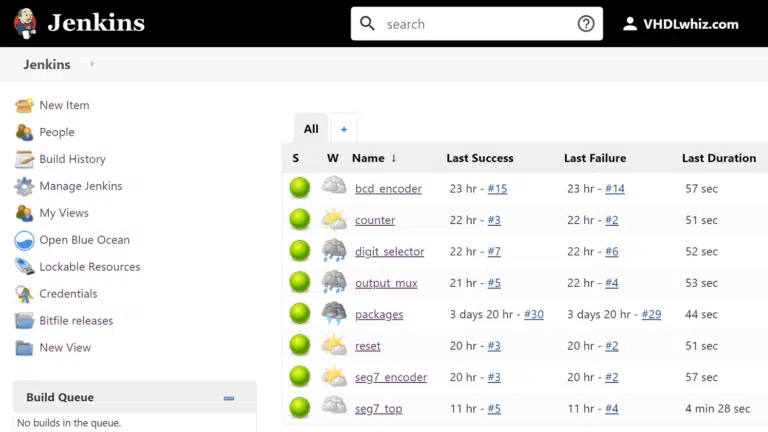

This tutorial teaches you how to set up an automation server on a Virtual Private Server (VPS) using Jenkins, Xilinx Vivado, and the Git / GitHub source-control management (SCM) system.

Jenkins can be a valuable tool also for FPGA teams. Automating tasks can save your company time and improve the quality of your code. By using automatic build triggers and automated job pipelines, fewer coding errors will go unnoticed.

Converting the image file to a bitmap format makes for the easiest way to read a picture using VHDL. Support for the BMP raster graphics image file format is built into the Microsoft Windows operating system. That makes BMP a suitable image format for storing photos for use in VHDL testbenches. In this article, you…

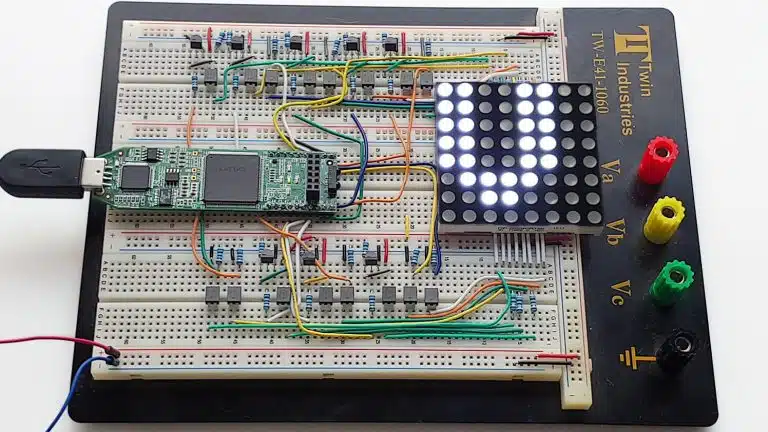

I’m excited to announce that the VHDL and FPGA course that I have been working on for the last six months is starting to become complete. The course is in beta at the moment, and I am planning on launching it for the first time this autumn. Who is the FPGA course for? The FPGA…

Constrained random verification is a testbench strategy that relies on generating pseudo-random transactions for the device under test (DUT). The goal is to reach functional coverage of a number of predefined events through random interaction with the DUT. Open Source VHDL Verification Methodology (OSVVM) is a free VHDL library which includes a number of convenient…

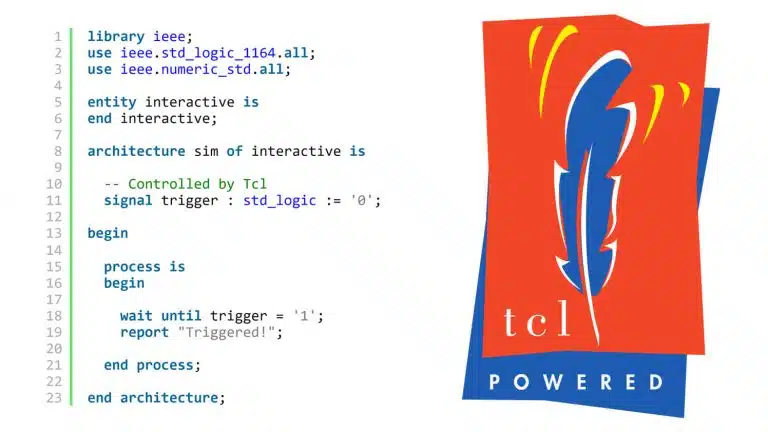

An interactive testbench is a simulator setup where input to the device under test (DUT) is provided by an operator while the testbench is running. Most often, this would mean you entering commands in the simulator console to provide the DUT with stimulus. While you should always create a self-checking testbench, an interactive testbench can…

The VHDL Analysis and Standardization Group (VASG), has been working for quite some time on finishing the draft for the upcoming VHDL-2019 revision of the language. The ballot has been held, and a list of approved changes has emerged. What’s left before this becomes the latest revision of the VHDL language is for the draft…

End of content

End of content