UVVM results in faster and better FPGA verification

How UVVM lets FPGA designers control multiple interfaces simultaneously in VHDL testbenches, reducing verification time and catching more bugs.

How UVVM lets FPGA designers control multiple interfaces simultaneously in VHDL testbenches, reducing verification time and catching more bugs.

This article is by guest author Dimitar Marinov, whom I (Jonas) contacted after seeing his excellent videos about DSP filters. You can read more about Dimitry below the blog post and find a link to his YouTube channel here. But first, read on to learn about complementary finite impulse response (FIR) filters!

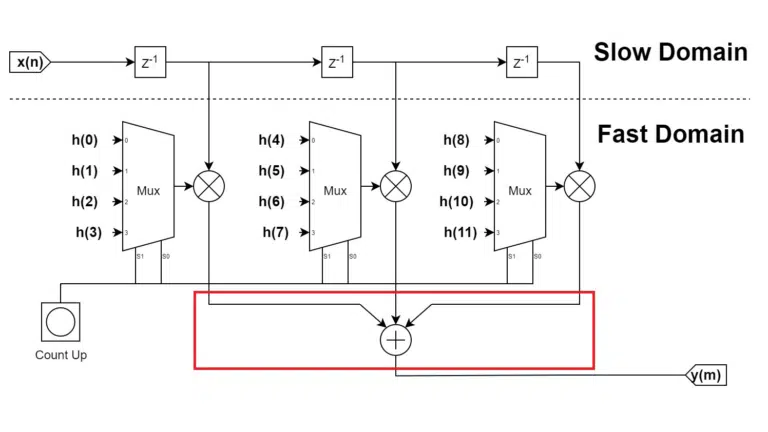

Polyphase filters are a class of specialized filters used in sample rate conversion. Whereas most FIR filters have one delay line, Polyphase filters have multiple. To understand the logic behind this, we’ll first have to dive into the topic of sample rate conversion.

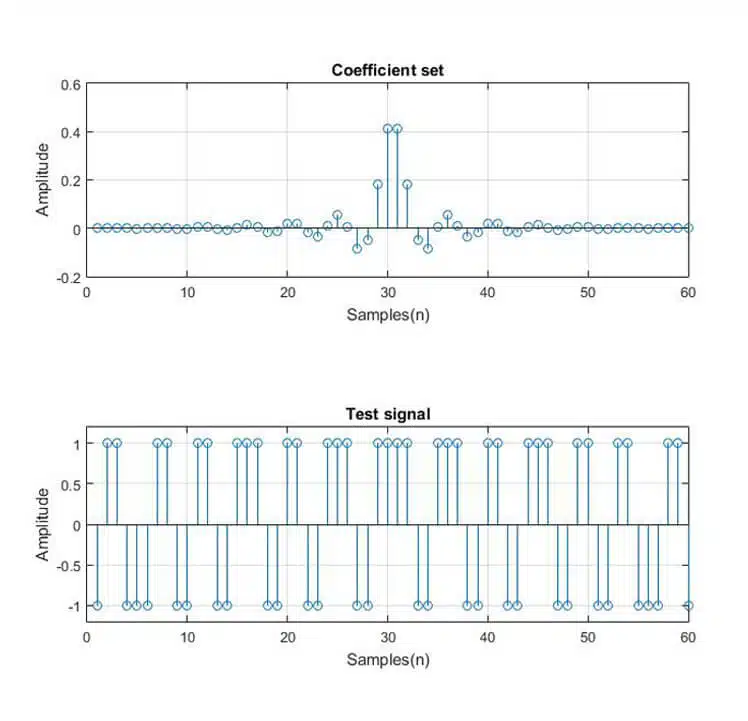

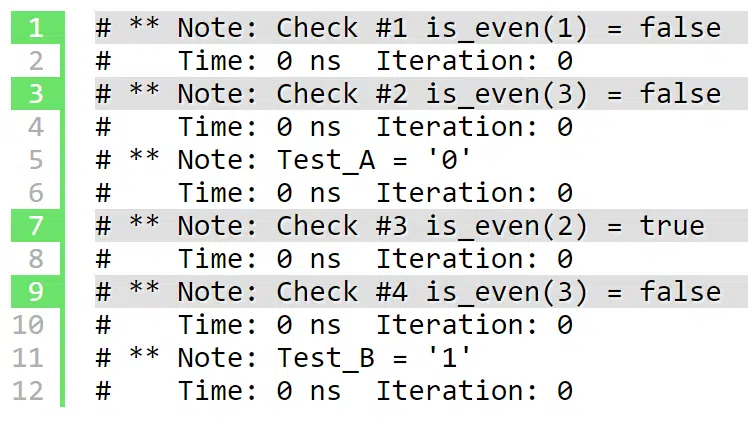

So far, the spotlight has fallen over the FIR filter design and its various forms. However, there is a problem that is just as important – how to ensure the implementation is working correctly. Whereas there are some standard techniques, it’s not always clear whether the design is error-proof. Therefore, this post discusses the most essential testing procedures and introduces a verification method that can easily incorporate them.

A binary operator is an operator that takes exactly two arguments. Examples of such are addition or multiplication and, of course, the familiar Boolean logical operators we use in VHDL: and, or nand nor xor and xnor.

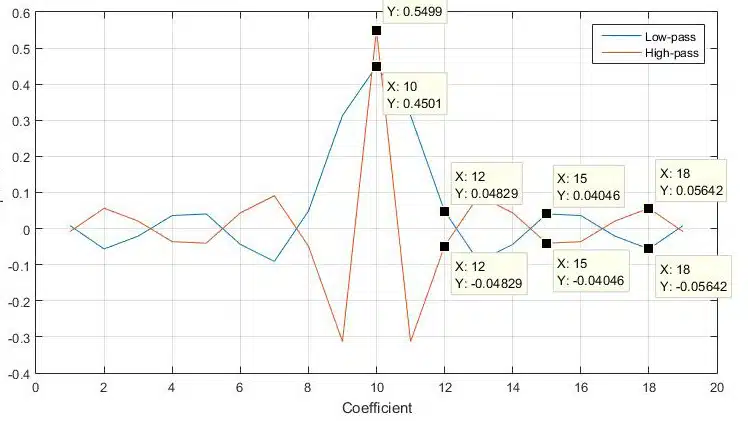

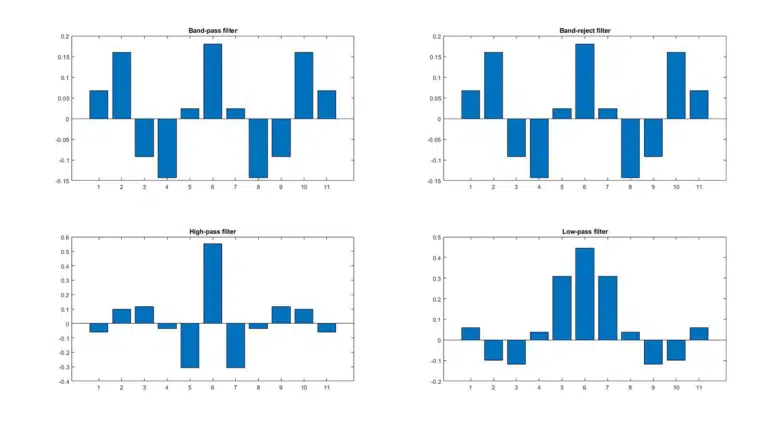

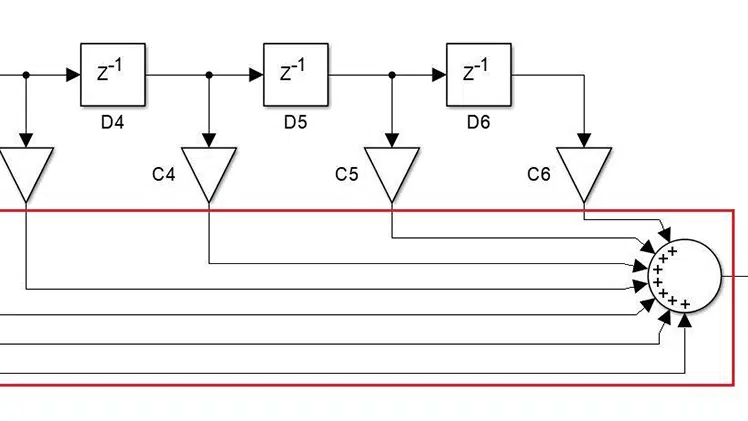

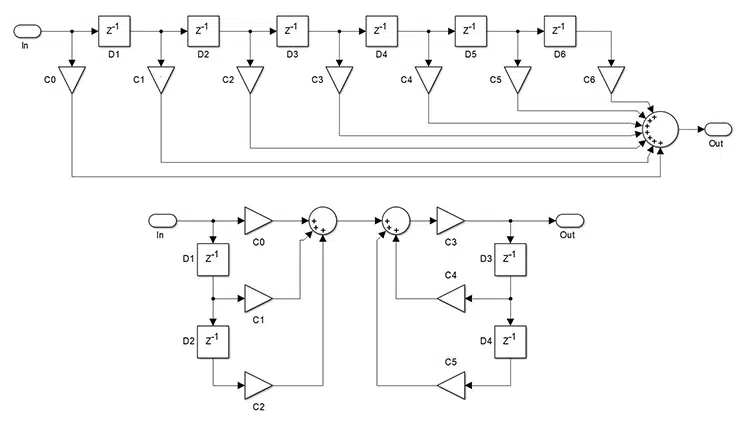

The previously discussed filter describes a general-purpose device that can fit in many applications but is not necessarily the optimal solution. This is where application-specific FIR structures come in. Therefore, this post aims to present some of the more popular filter structures used in specialized applications.

As an FPGA designer, you have the freedom to implement the (finite impulse response) FIR filter either parallel or in series. Read the article to find out how to implement a FIR filter using VHDL!

Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) are the two types of digital filters you’re most likely to use in FPGAs. This article discusses the implementation of the filters seen from the eyes of a hardware developer.

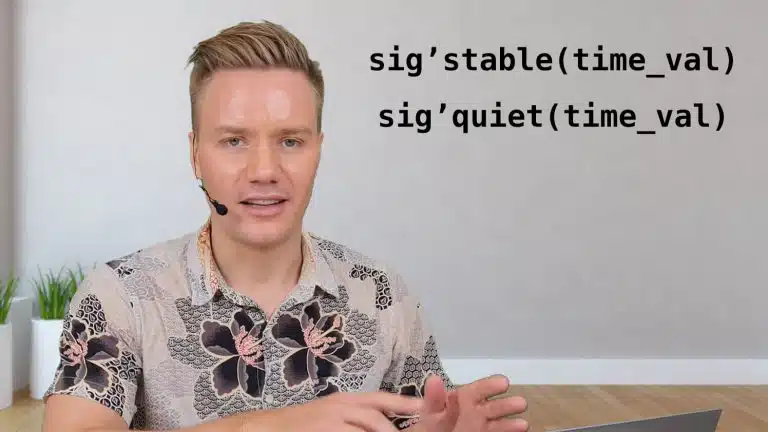

The ‘stable and ‘quiet attributes are predefined in the VHDL standard and work on signal objects. We can use these special features in simulation to check that a signal’s value remains untouched for a given period.

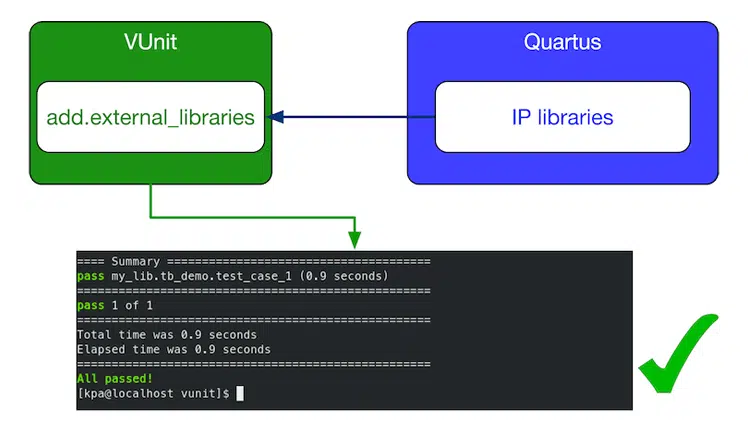

Have you ever wanted to run a VHDL simulation that includes a Quartus IP core through the VUnit verification framework?

This tutorial shows you how to generate, incorporate, and link external Quartus IP libraries to VUnit.

End of content

End of content