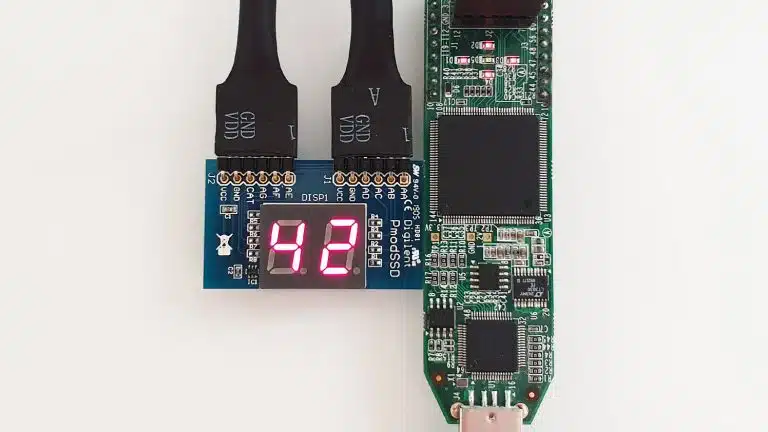

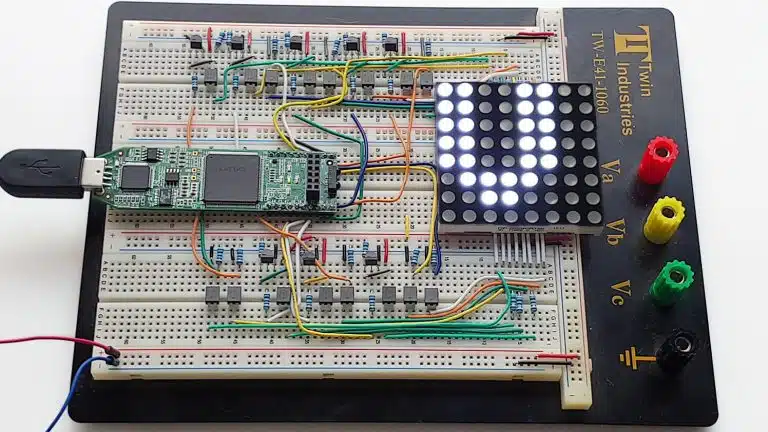

Dual 7-segment display FPGA controller

In this article, I will present a VHDL module that can display a two-digit number on the Pmod SSD: Seven-segment Display from Digilent. The dual 7-segment display is compatible with the Pmod interface, meaning that you can use it without any soldering. It fits into the Pmod connector, which is standard on many FPGA development boards.