I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to create a Tcl-driven testbench for a VHDL code lock module

Most VHDL simulators use the Tool Command Language (Tcl) as their scripting language. When you type a command in the console of the simulator, you are using Tcl. Furthermore, you can create scripts with Tcl that run in the simulator and interact with your VHDL code. In this article, we will create a self-checking testbench…

How to create a timer in VHDL

In earlier tutorials we have used the wait for statement to delay time in simulation. But what about production modules? The wait for statement cannot be used for that. That only works in simulation because we can’t just tell the electrons in a circuit to pause for a given time. So how can we keep…

How to create a process with a sensitivity list in VHDL

You should always use a sensitivity list to trigger processes in production modules. Sensitivity lists are parameters to a process which lists all the signals that the process is sensitive to. If any of the signals change, the process will wake up, and the code within it is executed. We’ve already learned to use the…

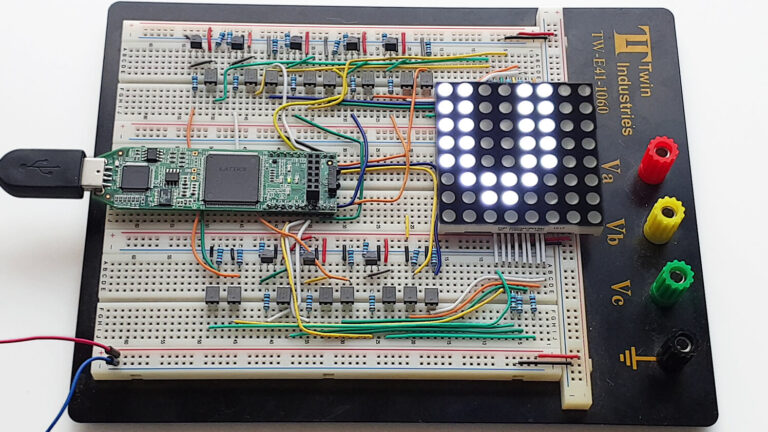

FPGA course – Everything you need to know about the Dot Matrix VHDL Course

I’m excited to announce that the VHDL and FPGA course that I have been working on for the last six months is starting to become complete. The course is in beta at the moment, and I am planning on launching it for the first time this autumn. Who is the FPGA course for? The FPGA…

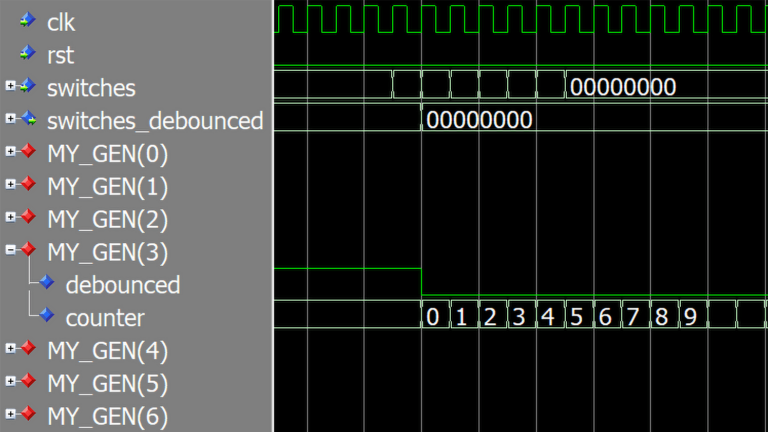

Generate statement debouncer example

The generate statement in VHDL can automatically duplicate a block of code to closures with identical signals, processes, and instances. It’s a for loop for the architecture region that can create chained processes or module instances.

Basic VHDL quiz – Part 1

Put your skills to the test with this quiz with questions from the first part of the Basic VHDL Tutorial series.

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.